Taoufik Bourdi, Izzet Kale9781402059278, 9781402059285, 1402059272, 0387321543, 9780387321547

This book is devoted to the subject of adaptive techniques for smart analog and mixed signal design whereby fully functional first-pass silicon is achievable. To our knowledge, this is the first book devoted to this subject. The techniques described should lead to quantum improvement in design productivity of complex analog and mixed signal systems while significantly cutting the spiraling costs of product development in emerging nanometer technologies. The underlying principles and design techniques presented are generic and would certainly apply to CMOS analog and mixed signal platforms in high volume , low-cost wireless , wire line, and consumer electronic SoC or chip set solutions.

Adaptive Techniques for Mixed Signal Sytem on Chip discusses the concept of adaptation in the context of analog and mixed signal design along with different adaptive architectures used to control any system parameter. The first part of the book gives an overview of the different elements that are normally used in adaptive designs including tunable elements as well as voltage, current, and time references with an emphasis on the circuit design of specific blocks such as voltage-controlled transconductors, offset comparators, and a novel technique for accurate implementation of on chip resistors. While the first part of the book addresses adaptive techniques at the circuit and block levels, the second part discusses adaptive equalization architectures employed to minimize the impact of ISI (Intersymbol Interference) on the quality of received data in high-speed wire line transceivers. It presents the implementation of a 125Mbps transceiver operating over a variable length of Category 5 (CAT-5) Ethernet cable as an example of adaptive equalizers.

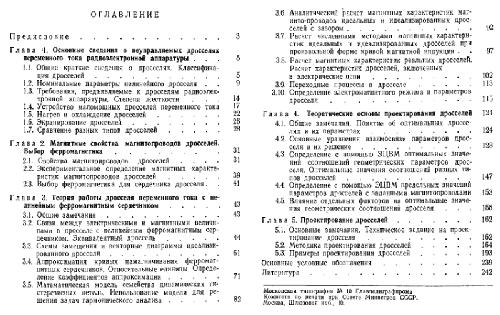

Table of contents :

CONTENTS……Page 6

PREFACE……Page 10

NOMENCLATURE……Page 12

1.1 Introduction……Page 14

1.2 Research Contribution……Page 15

2.1 Introduction……Page 19

2.2 The WLAN Standards……Page 20

2.3 WLAN Transceiver Systems……Page 22

2.3.2 The Receiver……Page 24

2.3.3 The Frequency Synthesizer (Local Oscillator)……Page 25

3.2 Phase-Locked Loop Frequency Synthesizer……Page 27

3.2.1 Phase-Locked Loop Main Blocks……Page 28

3.3 Phase-Locked Loop Parameters……Page 31

3.3.1 Loop Filter Design……Page 32

3.4 Noise in Phase-Locked Loops……Page 39

3.4.1 Component Noise Models……Page 41

3.5 Fractional-N Synthesizers……Page 46

3.5.1 Δ–Σ Modulators in Frequency Synthesizers……Page 48

3.6 RMS Phase Error (φ[sup(rms)]) and Error Vector Magnitude……Page 53

3.7 Conclusion……Page 54

4.1 Introduction……Page 57

4.2 Phase-Domain Model……Page 58

4.2.1 A Constituent Blocks Behavioral Models……Page 62

4.2.2 Noise Modeling Summary……Page 64

4.3 Synthesizer Platform Evaluation……Page 65

4.3.1 Dithering Effect……Page 69

4.3.3 Noise Folding……Page 72

4.3.4 Effect of Prescaler Divider……Page 74

4.4 Conclusion……Page 77

5.2 An overview……Page 78

5.3.1 Design Methodology……Page 80

5.4.1 The Phase-Frequency Detector……Page 82

5.4.2 The Charge Pump……Page 84

5.4.3 3.6 GHz Voltage-Controlled Oscillator……Page 96

5.4.4 The Multimodulus Divider……Page 100

5.4.5 The Fractional Noise Shaping Coder (the Δ–Σ Modulator)……Page 101

5.5 Measured Performance of the Implemented Synthesizer……Page 113

5.6 Summary and Conclusion……Page 118

6.2 Overview……Page 122

6.3.1 PLL Gain and Phase Variations……Page 124

6.3.2 Charge Pump System……Page 127

6.4 Synthesizer Loop Calibration……Page 128

6.5 Process Calibration I/C Slew Rate and RC Time Constant……Page 130

6.6.1 VCO Calibration Algorithm Description……Page 132

6.8 Experimental Results……Page 138

6.10 Conclusion……Page 139

7.1 Conclusion……Page 141

7.2 Further Work……Page 142

1 Phase-Frequency Detectors……Page 145

2 Charge Pump……Page 148

3 PFD/CP Characteristics……Page 150

1.1 Voltage-Controlled Crystal Oscillator……Page 152

1.2 Temperature-Compensated Crystal Oscillator……Page 154

2.1 Voltage-Controlled Oscillators: Phase Noise Analysis……Page 155

2.2 VCO Design Methodology……Page 158

1 Calculation of Global Phase Error From L(f)……Page 166

2 Phase Noise and Phase Modulation……Page 168

3 RMS Phase Error From Phase Noise……Page 170

4 Residual FM……Page 172

1.1 Synchronous Dividers……Page 173

1.2 Asynchronous Reference Frequency Divider……Page 174

2.1 Specification and Different Architecture Evaluation……Page 176

3 High-Speed CMOS Divider Design……Page 185

3.1 Current-Mode Logic Design: An Overview……Page 186

4 Implemented CML Gates……Page 191

1 Mathcad™ Program used for the Simulations of all the Mathcad Figures……Page 194

2 Matlab™ Program used for the Simulations of the Fractional-N PLL Noise Spectrum……Page 205

F……Page 214

W……Page 215

Reviews

There are no reviews yet.